Marco Danelutto Domenico Laforenza Marco Vanneschi (Eds.)

# Euro-Par 2004 Parallel Processing

10th International Euro-Par Conference Pisa, Italy, August/September 2004 Proceedings

### 3149

### Lecture Notes in Computer Science

Commenced Publication in 1973

Founding and Former Series Editors:

Gerhard Goos, Juris Hartmanis, and Jan van Leeuwen

### **Editorial Board**

David Hutchison

Lancaster University, UK

Takeo Kanade

Carnegie Mellon University, Pittsburgh, PA, USA

Josef Kittler

University of Surrey, Guildford, UK

Jon M. Kleinberg

Cornell University, Ithaca, NY, USA

Friedemann Mattern

ETH Zurich, Switzerland

John C. Mitchell

Stanford University, CA, USA

Moni Naor

Weizmann Institute of Science, Rehovot, Israel

Oscar Nierstrasz

University of Bern, Switzerland

C. Pandu Rangan

Indian Institute of Technology, Madras, India

Bernhard Steffen

University of Dortmund, Germany

Madhu Sudan

Massachusetts Institute of Technology, MA, USA

Demetri Terzopoulos

New York University, NY, USA

Doug Tygar

University of California, Berkeley, CA, USA

Moshe Y. Vardi

Rice University, Houston, TX, USA

Gerhard Weikum

Max-Planck Institute of Computer Science, Saarbruecken, Germany

Marco Danelutto Domenico Laforenza Marco Vanneschi (Eds.)

## Euro-Par 2004 Parallel Processing

10th International Euro-Par Conference Pisa, Italy, August 31- September 3, 2004 Proceedings eBook ISBN: 3-540-27866-4 Print ISBN: 3-540-22924-8

©2005 Springer Science + Business Media, Inc.

Print ©2004 Springer-Verlag Berlin Heidelberg

All rights reserved

No part of this eBook may be reproduced or transmitted in any form or by any means, electronic, mechanical, recording, or otherwise, without written consent from the Publisher

Created in the United States of America

Visit Springer's eBookstore at: http://ebooks.springerlink.com and the Springer Global Website Online at: http://www.springeronline.com

### **Preface**

### **Euro-Par Conference Series**

Euro-Par is an annual series of international conferences dedicated to the promotion and advancement of all aspects of parallel computing. The major themes can be divided into the broad categories of hardware, software, algorithms and applications for parallel computing. The objective of Euro-Par is to provide a forum within which to promote the development of parallel computing both as an industrial technique and an academic discipline, extending the frontier of both the state of the art and the state of the practice. This is particularly important at a time when parallel computing is undergoing strong and sustained development and experiencing real industrial take-up. The main audience for, and participants at, Euro-Par are seen as researchers in academic departments. government laboratories and industrial organizations. Euro-Par's objective is to be the primary choice of such professionals for the presentation of new results in their specific areas. Euro-Par also targets applications demonstrating the effectiveness of parallelism. This year's Euro-Par conference was the tenth in the conference series. The previous Euro-Par conferences took place in Stockholm, Lyon, Passau, Southampton, Toulouse, Munich, Manchester, Paderborn and Klagenfurt. Next year the conference will take place in Lisbon. Euro-Par has a permanent Web site hosting the aims, the organization structure details as well as all the conference history: http://www.europar.org. Currently, the Euro-Par conference series is sponsored by the Association for Computing Machinery (ACM) in cooperation with SIGACT, SIGARCH and SIGMM, by the International Federation for Information Processing (IFIP) in cooperation with IFIP WG 10.3, and by the Institute of Electrical and Electronics Engineers (IEEE) in cooperation with TCPP.

### Euro-Par 2004 at Pisa, Italy

Euro-Par 2004 was organized by the University of Pisa, Department of Computer Science and by the National Research Council Institute of Information Science and Technologies (ISTI), also located in Pisa. The conference took place at the "Palazzo dei Congressi" (the Conference Center of Pisa University). A number of tutorials and invited talks extended the regular scientific program. The tutorials and the invited talks covered major themes in the current high-performance parallel computing scenarios:

The full-day tutorial "Open Source Middleware for the Grid: Distributed Objects and Components in ProActive", by Denis Caromel (OASIS, INRIA Sophia Antipolis, France) covered major aspects in the implementation of middleware supporting the development of grid applications through suitable, open-source, component-based middleware.

- The half-day tutorial "Achieving Usability and Efficiency in Large-Scale Parallel Computing Systems" by Fabrizio Petrini and Kei Davis (Los Alamos National Laboratory, USA) went through the techniques used to set up high-performance clusters exploiting the most recent and advanced interconnection technology.

- The half-day tutorial "Grid Resource Management and Scheduling", by Ramin Yahyapour (University of Dortmund, Germany) presented an overview of the state of the art and experiences in Grid resource management and scheduling.

- The invited talk by Dennis Gannon (Indiana University, USA) "Building Grid Applications and Portals: An Approach Based on Components, Web Services and Workflow Tools" dealt with advanced techniques for building grid applications.

- The invited talk by Manuel Hermenegildo (Technical University of Madrid and University of New Mexico) "Some Techniques for Automated, Resource-Aware Distributed and Mobile Computing in a Multi-paradigm Programming System" dealt with advanced techniques for distributed and mobile computing.

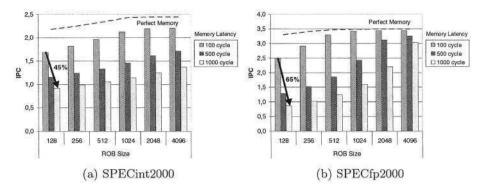

- The invited talk by Mateo Valero (DAP-UPC Barcelona, Spain) "Kilo-instruction Processors" was about innovative processor technology aimed at reducing the problems raised by memory access latency.

- Last but not least, the invited talk by Murray Cole (School of Informatics, Edinburgh, UK) "Why Structured Parallel Programming Matters" was focused on the relevance and effectiveness of structured parallel programming with respect to performance, correctness and productivity.

The tutorials all took place on Tuesday, 31st of August. Two invited talks were scheduled for the beginning of the regular scientific program of the conference, on Wednesday, 1st of September, and two were scheduled for the end, on Friday, 3rd of September.

### **Euro-Par 2004 Statistics**

Euro-Par 2004 followed the classic Euro-Par conference format and consisted of a number of topics. Each topic was supervised by a committee of four persons: a global chair, a local chair and two vice chairs. This year the conference ran 19 different topics. In addition to classic Euro-Par topics, the High-Performance Bioinformatics topic was introduced for the first time. A Demo Session topic included in the conference program after the positive experience of Euro-Par 2003 received a very small number of submissions. It was eventually canceled from the conference program and the accepted submissions were moved to another, related topic. The overall call for papers was closed in early February 2004 and attracted a total of 352 submissions; 124 papers were accepted after a refering process that collected an average 3.6 referee reports per paper, for a grand total of more than 1300 referee reports that involved more than 600 different reviewers; 105 papers

were accepted as regular papers, 15 as research notes, and 4 as distinguished papers. Eventually, 2 papers were withdrawn by the authors, and therefore 122 papers are actually included in these proceedings. Papers were submitted from 39 different countries, according to the corresponding author country. Papers were accepted from 27 different countries. The major number of accepted papers came from the USA (22 papers), France and Spain (15 papers each), and Germany and Italy (13 papers each).

### Acknowledgments

Different institutions and a number of individuals contributed to Euro-Par 2004 in different ways. The University of Pisa, its Computer Science Department, the National Research Council (CNR) and the ISTI (Institute of Information Science and Technologies) were the main conference institutional sponsors. A number of different industrial sponsors gave their contributions and/or participated in organizing the industrial booths at the conference location. Their names and logos are all collected on the Euro-Par 2004 conference Web site: http://www.di.unipi.it/europar04. A special thanks is due to the authors of the submitted papers as well as to the topic committee members and to the reviewers who overall contributed to making this conference possible. Also, the organizing committee thanks the Euro-Par steering committee for the continuous support during the conference organization. Special support was provided by Christian Lengauer, chair of the steering committee and by Harald Kosch, co-organizer of the 2003 Euro-Par conference. A special thanks is for the local organization team, Sonia Campa, Nicola Tonellotto, Marco Aldinucci, Massimo Coppola, Tiziano Fagni, Alessandro Paccosi, Antonio Panciatici, Diego Puppin, and Fabrizio Silvestri, and for the NORCI team, which solved many problems related to the conference organization and set up.

We all hope that the attendees had a pleasant stay in Pisa at the Euro-Par 2004 conference!

Pisa. June 2004

Marco Danelutto Domenico Laforenza Marco Vanneschi

### **Euro-Par Steering Committee**

### Chair

Christian Lengauer University of Passau, Germany

Vice Chair

Luc Bougé ENS Cachan, France

**European Representatives**

Marco Danelutto University of Pisa, Italy

Rainer Feldmann University of Paderborn, Germany Christos Kaklamanis Computer Technology Institute, Greece

Harald Kosch

Paul Kelly

Thomas Ludwig

University of Klagenfurt, Austria

Imperial College, United Kingdom

University of Heidelberg, Germany

Emilio Luque Universitat Autònoma of Barcelona, Spain University of Southampton, United Kingdom University of Manchester, United Kingdom Technical University Delft, The Netherlands

**Non-European Representatives**

Jack Dongarra University of Tennessee at Knoxville, USA

Shinji Tomita Kyoto University, Japan

**Honorary Members**

Ron Perrott Queen's University Belfast, United Kingdom Karl Dieter Reinartz University of Erlangen-Nuremberg, Germany

Observers

José Cunha New University of Lisboa, Portugal

### **Euro-Par 2004 Local Organization**

Euro-Par 2004 was organized by the University of Pisa, Department of Computer Science and by the Italian National Research Council Institute of Information Science and Technologies.

### **Conference Chair**

Marco Danelutto Domenico Laforenza Marco Vanneschi

### **Committee**

Sonia Campa Marco Aldinucci Massimo Coppola Tiziano Fagni Alessandro Paccosi Antonio Panciatici Diego Puppin Fabrizio Silvestri Nicola Tonellotto

Lita Sabini

### **Euro-Par 2004 Programme Committee**

### **Topic 1: Support Tools and Environments**

Global Chair

José C. Cunha Faculdade de Ciências e Tecnologia

Universidade Nova de Lisboa, Portugal

Local Chair

Dieter Kranzlmüller Institut für Technische Informatik und

Telematik Johannes Kepler Universität

Linz, Austria

Vice Chairs

Allen Malony Department of Computer and Information

Science University of Oregon, USA

Arndt Bode Institut für Informatik, Technische

Universität München, Germany

### **Topic 2: Performance Evaluation**

Global Chair

Wolfgang E. Nagel Center for High Performance Computing,

Technical University Dresden, Germany

**Local Chair**

Lorenzo Donatiello Department of Computer Science,

University of Bologna, Italy

Vice Chairs

Thomas Ludwig Institute of Computer Science,

Ruprecht-Karls-Universität Heidelberg,

Germany

Jeffrey Vetter Oak Ridge National Laboratory,

Oak Ridge, USA

### Topic 3: Scheduling and Load Balancing

Global Chair

Emilio Luque Dept. Computer Science,

Universitat Autònoma de Barcelona, Spain

Local Chair

Raffaele Perego ISTI-CNR Pisa, Italy

Vice Chairs

Evangelos Markatos Institute of Computer Science (ICS),

Crete, Greece

José G. Castanos IBM Thomas J. Watson Research Center,

New York, USA

### **Topic 4: Compilers for High Performance**

### Global Chair

Hans P. Zima Institute for Software Science, University

of Vienna, Austria, and Jet Propulsion

Laboratory, California Institute

of Technology, Pasadena, California, USA

**Local Chair**

Beniamino Di Martino Department of Information Engineering,

Second University of Naples, Italy

Vice Chairs

Siegfried Benkner Institute for Software Science,

University of Vienna, Austria

Michael O'Boyle University of Edinburgh, UK

### Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery

### **Global Chair**

David Skillicorn School of Computing, Queen's University,

Kingston, Ontario, Canada

**Local Chair**

Salvatore Orlando Department of Computer Science,

University of Venice, Italy

Vice Chairs

Abdelkader Hameurlain IRIT, Université Paul Sabatier, Toulouse,

France

Paul Watson School of Computing Science, University

of Newcastle upon Tyne, United Kingdom

### Topic 6: Grid and Cluster Computing

### **Global Chair**

Thierry Priol IRISA/INRIA, Rennes, France

Local Chair

Diego Puppin ISTI/CNR, Pisa, Italy

Vice Chairs

Craig Lee Aerospace Corporation, El Segundo,

USA

Uwe Schwiegelshohn University of Dortmund, Germany

### **Topic 7: Applications on High-Performance Computers**

Global Chair

Jack Dongarra Computer Science Department,

University of Tennessee, USA

**Local Chair**

Rolf Hempel German Aerospace Center DLR, Cologne,

Germany

Vice Chairs

David W. Walker Department of Computer Science,

University of Wales, Cardiff, UK

Peter Arbenz Institute of Computational Science,

Zürich, Switzerland

### Topic 8: Parallel Computer Architecture and Instruction-Level Parallelism

Global Chair

Kemal Ebcioglu IBM T.J. Watson Research Center,

New York, USA

**Local Chair**

Marco Aldinucci ISTI-CNR, Pisa, Italy

Vice Chairs

Wolfgang Karl Institut für Rechnerentwurf und

Fehlertoleranz,

Universität Karlsruhe (TH), Germany

André Seznec IRISA, Campus de Beaulieu, Rennes,

France

### **Topic 9: Distributed Algorithms**

Global Chair

Henri Bal Dept. Computer Science,

Vrije Universiteit, Amsterdam,

The Netherlands

**Local Chair**

Giuseppe Prencipe Department of Computer Science,

University of Pisa, Italy

Vice Chairs

Andrzej M. Goscinski School of Information Technology,

Deakin University, Victoria, Australia

Eric Jul Dept. of Computer Science,

University of Copenhagen, Denmark

### Topic 10: Parallel Programming: Models, Methods and Programming Languages

**Global Chair**

Paul H.J. Kelly Department of Computing,

Imperial College of Science,

Technology and Medicine, London, UK

**Local Chair**

Sergei Gorlatch Institut für Informatik,

Universität Münster, Germany

Vice Chairs

Daniel Quinlan Center for Applied Scientific Computing,

Lawrence Livermore National Laboratory.

Livermore, USA

Linköpings Universitet, Sweden

### **Topic 11: Numerical Algorithms**

Global Chair

Emilio L. Zapata Dept. of Computer Architecture,

University of Malaga, Spain

Local Chair

Pasqua D'Ambra ICAR-CNR, Naples, Italy

Vice Chairs

Oscar Plata Dept. of Computer Architecture,

University of Malaga, Spain

David Keyes Dept. of Appl. Physics

and Appl. Mathematics,

Columbia University, New York, USA

### **Topic 12: High-Performance Multimedia**

Global Chair

Odej Kao Department of Computer Science,

University of Paderborn, Germany

Local Chair

Harald Kosch Institute of Information Technology,

University of Klagenfurt, Austria

Vice Chairs

Anreas Uhl Department of Scientific Computing,

University of Salzburg, Austria

Subramania Sudharsanan Queen's University, Kingston, Ontario,

Canada

### **Topic 13: Theory and Algorithms for Parallel Computation**

Global Chair

Christos Kaklamanis Computer Technology Institute

and Department of Computer Engineering & Informatics, University of Patras, Greece

Local Chair

Andrea Pietracaprina Department of Information Engineering,

University of Padova, Italy

Vice Chairs

Nancy Amato Department of Computer Science,

Texas A&M University, USA

Danny Krizanc Mathematics Department,

Wesleyan University, Middletown,

Connecticut, USA

### Topic 14: Routing and Communication in Interconnection Networks

**Global Chair**

José Duato Technical University of Valencia, Spain

**Local Chair**

Fabrizio Petrini Los Alamos National Laboratory, USA

Vice Chairs

Olav Lysne Simula Research Lab

and University of Oslo, Norway

Angelos Bilas University of Crete, Greece

### **Topic 15: Mobile Computing**

Global Chair

Sajal K. Das Center for Research in Wireless Mobility

and Networking (Crewman), University

of Texas at Arlington, Texas, USA

**Local Chair**

Gianluigi Ferrari Department of Computer Science,

University of Pisa, Italy

Vice Chairs

Jiannong Cao Hong Kong Polytechnic University,

Hong Kong

Jie Wu Florida Atlantic University, USA

### **Topic 16: Integrated Problem-Solving Environments**

**Global Chair**

Domenico Talia DEIS, University of Calabria, Rende (CS), Italy

Local Chair

Daniela Di Serafino Department of Mathematics,

Second University of Naples, Italy

Vice Chairs

Peter Sloot Faculty of Science, University

of Amsterdam, The Netherlands

Elias Houstis Department of Computer

and Communications Engineering, University of Thessaly, Volos, Greece, and Department of Computer Sciences Purdue University,

West Lafayette, IN, USA

### **Topic 17: High-Performance Bioinformatics**

Global Chair

Mohammed J. Zaki Department of Computer Science,

Rensselaer Polytechnic Institute,

Troy, NY, USA

Local Chair

Concettina Guerra Department of Computer Engineering,

University of Padova, Italy

Vice Chairs

David A. Bader Electrical and Computer Engineering

Department, University of New Mexico,

Albuquerque, USA

Johan Montagnat Creatis, INSA, Villeurbanne, France

### **Topic 18: Peer-to-Peer Computing**

Global Chair

Seif Haridi Department of Computer Science, National

University of Singapore, Singapore

**Local Chair**

Michele Colajanni Department of Engineering Science,

University of Modena and Reggio Emilia,

Modena, Italy

Vice Chairs

Karl Aberer Institute for Core Computing Science

(IIF), School for Computer

and Communication Science (I&C).

Lausanne, Switzerland

Peter Van Roy Department of Computing Science

and Engineering, Catholic University of Louvain, Louvain-la-Neuve, Belgium

### **Topic 19: Demo Session**

**Global Chair**

Henk J. Sips Department of Computer Science, Delft

University of Technology, The Netherlands

**Local Chair**

Massimo Coppola Department of Computer Science,

University of Pisa, Italy

Vice Chairs

Luc Moreau University of Southampton, UK

Bernd Mohr Research Center Juelich, Juelich, Germany

### Euro-Par 2004 Referees

(not including members of the programme or organization committees)

Abella, Jaume

Acher, Georg

Agrawal, Gagan

Aida, Kento

Aldinucci, Marco

Almasi, George

Alt, Martin

Aluru, Srinivas

Amamiya, Satoshi

Amherst, Umass

Andreolini, Mauro

Antoniu, Gabriel

Apostolopoulos, George

Arbenz, Peter Arioli, Mario Asenjo, Rafael Ashby, Tom Attanassio, Dick Avis, Nick J. Badia, Rosa M. Baggio, Aline

Bagherzadeh, Nader Baiardi, Fabrizio Baker, Mark Bal, Henri

Banâtre, Jean-Pierre

Bandera, G.

Banerjee, Nilanjan Basermann, Achim Beck, Micah

Beck, Mican Beckmann, Olav Beivide, Ramon Bell, Robert Benkner, Siegfried Beraldi, Roberto Bern, Marshall Bertoldo, Alberto Bilas, Angelos Bischof, Holger Bisseling, Rob H. Bode, Arndt Bodin, Francois Bokhari, Shahid Bononi, Luciano Borgeest, Rolf Brandes, Thomas Brandic, Ivona Bravetti, Mario Breton, Vincent Bretschneider, Timo Brezany, Peter Browne, Jim

Bruguera, Javier D. Brunst, Holger

Bucchignani, Edoardo

Buchty, Rainer

Budé, Porfidio Hernández

Buyya, Rajkumar Cabri, Giacomo

Caceres, Edson Norberto

Cafaro, Massimo Campa, Sonia Camus, Herve Canali, Claudia Cao, Chun Cao, Jiannong Cappello, Franck Caragiannis, Ioannis Cardei, Mihaela Cardellini, Valeria Carissimi, Alexandre Caruso, Antonio Casado, L.G. Casanova, Henri Cascaval, Calin Casola, Valentina Castanos, Jose

Castanos, Jose Ceccanti, Andrea Ceccarelli, Michele Cela, Jose M.

Chakravarty, Manuel Chalabine, Mikhail

Chapman, Barbara

Chassin de Kergommeaux, Jacques

Chatzigiannakis, Ioannis

Chbeir, Richard Cheng, Perry Chessa, Stefano

Choi, Tae-Uk

Choi, Wook Chung, I-Hsin Ciriani, Valentina Clematis, Andrea

Codina, Josep M. Colajanni, Michele Collet, Raphael Congiusta, Antonio Coppola, Massimo Corsaro, Stefania Cortes, Ana

Courtiat, Jean-Pierre Cremet, Vincent Cunha, Jose C. Cuppens, Frédéric Czajkowski, Karl Czech, Zbigniew J. D'Agostino, Daniele D'Ambra, Pasqua D'Angelo, Gabriele Dahlgren, Tamara

Dahm, Ingo Dail, Holly Dalgic, Ismail Danelutto, Marco

Das, Sajal

Dash, Manoranjan

Davis, Kei Davoli, Renzo Daydé, Michel

de Sola, Francesc Giné de Supinski, Bronis R.

Deb, Kalyanmoy Deelman, Ewa Delmastro, Franca Dew, Robert

di Serafino, Daniela Dias, Artur M. Dimakopoulos, Vassilios V.

Doallo, R. Dogan, Atakan Dolbeau, Romain Drozdowski, Maciej

Duato, José Duennweber, Jan

Eisenbach, Susan El-Ansary, Sameh Elbern, Hendrik Engelbrecht, Gerhard

Epema, Dick Epperly, Tom Ernemann, Carsten Erway, Charles Esener, Sadik Evripidou, Skevos

Faber, Peter

Fagni, Tiziano

Fernandez, J.J.

Ferrari, Gianluigi

Ferretti, Stefano

Ferrini, Renato

Figueiredo, Renato

Filippone, Salvatore

Flocchini, Paola

Folino, Gianluigi

Fraboulet, Antony

Franco, Daniel

Franke, Bjoern

Franke, Hubertus

Friebe, Lars

Frolov, Pavel

Fürlinger, Karl

Fursin, Grigori

Galizia, Antonella

Gannon, Dennis

Garcia, Inmaculada

Garzon, E.M.

Gazzaniga, Giovanna

Geisler, Stefan Gennaro, Claudio Gerlach, Jens Gerndt, Michael Gervasi, Vincenzo

### XVIII Organization

Getov, Vladimir Ghini, Vittorio Ghodsi, Ali

Gil-García, Reynaldo Girdzijauskas, Sarunas

Glynn, Kevin

Gómez, María Engracia

Gorlatch, Sergei

Goscinski, Andrzej M.

Gottschling, Peter Grauer, Manfred Griebl, Martin Grigoras, Romulus Grimstead, Ian J. Grolaux, Donatien

Grove, David Gschwind, Michael Guarracino, Mario Guerra, Concettina Gupta, Anshul Gusat, Mitchell Gutierrez, Eladio

Hameurlain, Abdelkader Hansen, Audun Fosselie

Haridi, Seif Hartstein, Allan Harz, Wolf-Dietrich Hellwagner, Hermann

Hempel, Rolf

Herrmann, Christoph Heydemann, Karine Heymann, Elisa Hobbs, Michael

Hochberger, Christian

Hofstedt, Petra Hollingsworth, Jeff Homburg, Philip Horn, Geir Houstis, Elias Huet, Fabrice Inostroza, Mario Jefferson, David Jégou, Yvon

Jeitner, Jürgen

Jesshope, Chris

Ji, Yongchang

Jin, Hai

Johnsen, Einar Broch

Johnson, Chris Jones, Tim Jorda, Jacques Joshi, Anupam Kao, Odej

Karakostas, Georgios Karczmarek, Michal Karonis, Nicholas Katevenis, Manolis

Keane, John Kelly, Paul Kenyon, Chris Kerbyson, Darren Kereku, Edmond Kersken, Hans-Peter Kessler, Christoph

Keyes

Kielmann, Thilo Klasing, Ralf Kleinjung, Jens Knijnenburg, Peter

Knoop, Jens

Kosch, Harald

Koziris, Nectarios

Kranzlmüller, Dieter

Krechel, Arnold

Krizanc, Danny

Kuchen, Herbert

Kudriaytsey, Alexei

Kudriavtsev, Alexei Kumar, Raj Kumar, Sanjeev Kumfert, Gary Kyriacou, Costas Laccetti, Giuliano Lacour, Sébastien Lafage, Thierry Laforenza, Domenico Lakamraju, Vijay Lamont, Gary Lancellotti, Riccardo Lanteri, Stéphane

Lauria, Mario

Lecussan, Bernard Lee, Craig

Lee, Jack Lee, Pete

Legrand, Arnaud Leong, Hong-Va Leshchinskiy, Roman

Li, Kai Li, Tianchao Li. Vivian Li, Yaohang Lipasti, Mikko Lodi, Giorgia Lombardo, Saverio Lonetti, Francesca Lopes, Paulo Lopez, Pedro

Lou. Wei

Loulergue, Frederic

Lottiaux, Renaud

Lowe, Welf

Lucchese, Claudio Ludwig, Thomas Luque, Emilio Lysne, Olav Maassen, Jason

Machì, Alberto MacLaren, Jon Madria, Sanjay Maehle, Eric Magklis, Gregory

Magoutis, Kostas

Maheswaran, M.

Mairandres, Martin Maloney, Andrew Malony, Allen D. Mandal, Anirban Marazakis, Manolis Margalef, Tomas Marinescu, Dan Markatos, Evangelos Martin, Maria J.

Martoglia, Riccardo Martorell, Xavier Maselli, Gaia

Masuzawa, Toshimitsu

Mattsson, Hakan Matvska, Ludek

May, John

Medeiros, Pedro Mehammed, Hamza Mehofer, Eduard Mehra, Pankaj Melhem, Rami

Mellia, Marco Mendes, Celso L. Merzky, Andre Mesaros, Valentin Mezzetti. Nicola

Michaud, Pierre Miguel-Alonso, Jose Mihailovic, Milan Miller, Patrick

Mix. Hartmut Mohr, Bernd

Monnet, Sébastien Montagnat, Johan Montella, Raffaele Montresor, Alberto

Moreau, Luc Moreira, Jose

Moscato, Francesco Moshovos, Andreas Moulitsas, Irene Mucci, Phil Mullai, Srinivasan

Müller-Pfefferkorn, Ralph

Mutlu, Onur

Nagel, Wolfgang E. Nakada, Hidemoto Nakhimovski, Iakov Namyst, Raymond Naroska, Edwin Nenadic, Goran Networks, Redback Nguyen, Thu D.

Ni, Yang

Niculescu, Virginia Nigel, Thomas Nolte, Joerg

### XX Organization

O'Boyle, Michael Obertelli, Graziano Oklobdzija, Vojin Oliker, Leonid Omang, Knut Overeinder, Benno Ozguner, Fusun

Paccosi, Alessandro

Pagani, Elena

Pagli, Linda

Paker, Yakup

Pakin, Scott

Palazzari, Paolo

Palazzi, Claudio

Panda, D.K.

Papadopoulos, Constantinos

Papaioannou, Evi Parashar, Manish Park, Seungjin Park, Y.W.

Parthasarathy, Srinivasan

Pazat, Jean-Louis

Pelagatti, Susanna

Perego, Raffaele

Pérez, Christian

Perla, Francesca

Petrini, Fabrizio

Pflüger, Stefan

Pierre, Guillaume

Pierson, Jean-Marc

Pietracaprina, Andrea

Pietracaprina, Al Pinotti, Cristina Pirsch, Peter Plale, Beth Plank, James S. Plata, Oscar

Pnevmatikatos, Dionisios

Podlipnig, Stefan Pokam, Gilles Pozniansky, Eli Prencipe, Giuseppe Prieto, Manuel

Primet, Pascale Vicat-Blanc

Priol, Thierry Pucci, Geppino Pugliese, Andrea Puppin, Diego Quinlan, Dan Rajic, Hrabri L. Ralha, Rui

Ramakrishnan, Naren

Rana, Omer F. Rastello, Fabrice Rathmayer, Sabine Rauber, Thomas Raynal, Michel Reinemo, Sven-Arne

Ricci, Laura Ripoll, Ana

Rivera, Francisco F.

Robert, Yves Robles, Antonio Roccetti, Marco Roig, Concepció Romero, Felipe Rossi, Davide Rothkrantz, Leon Roussopoulos, Mema Ruenger, Gudula Ryan, Stein Jørgen Sainrat, Pascal Sakellariou, Rizos Sánchez, Jesús Sancho, José Carlos Sander, Volker Sanders, Peter Sane, Aamod Santos, Luis Paulo Sathave, Sumedh Scheuermann, Peter Schimpf, Joachim Schintke, Florian Schmermbeck, Stefan Schmidt, Andreas C. Schmidt, Bertil

Schoettner, Michael Schojer, Peter Schordan, Markus Schramm, Peter Schueller, Anton Schulz, Martin Schütt, Thorsten Schwiegelshohn, Uwe Senar, Miquel A. Sergeyev, Yaroslav D.

Serot, Jocelyn Serpanos, Dimitrios

Sevcik, Ken Seymour, Keith Seznec, André Shan, Hongzhang

Shen, Kai Shende, Sameer Shestak, Vladimir

Shestak, Vladimir Sie, H.J. Silcock, Jackie Silla, Federico Silva, Fernando Silva, Joao Gabriel Silva, Luis Moura Silvestri, Claudio Silvestri, Fabrizio Simmel, Derek Singer, Daniel

Skeie, Tor Skillicorn, David Smith, Jim Sobe, Peter Solihin, Yan Solsona, Francesc

Singh, Arjun

Sips, Henk J.

Song, S.W.

Spezzano, Giandomenico

Spielman, Daniel Stiliadis, Dimitrios Stockinger, Heinz Streit, Achim Strohmaier, Erich Stunkel, Craig

Su, Alan

Sudharsanan, S.

Sugavanam, Prasanna V.

Talia, Domenico

Tao, Jie

Taylor, Ian J. Terpstra, Dan Theiss, Ingebjorg Theys, Mitchell D.

Thiyagalingam, Jeyarajan

Tierney, Brian

Tikir, Mustaka

Tjortjis, Christos

Tonellotto, Nicola

Toraldo, Gerardo

Touati, Sid

Toulouse, Michel

Trabado, Guillermo P.

Trenkler, Bernd

Trinitis, Carsten Trunfio, Paolo Truong, Hong-Linh Trystram, Denis Tseng, Chau-Wen Tulone, Daniela Tuosto, Emilio Turek, Stefan Turi, Giovanni Ubik, Sven

Uhl. Andreas

Ungerer, Theo

Ungor, Alper Urpi, Alessandro van den Berghe, Sven van Nieuwpoort, Rob van Reeuwijk, Kees van Renesse, Robbert

Van Roy, Peter Vanneschi, Marco Venticinque, Salvatore Verdoscia, Lorenzo Vetter, Jeffrey Villalba, Julio Vogels, Werner Volpato, Alessandra von Laszewski, Gregor von Praun, Christoph

Vukovic, Jaksa Wagner, Gustavo Walker, David W.

### XXII Organization

Watson, Paul

Weerawarana, Sanjiva

Weidendorfer, Josef

White, Brian

White, James B., III

Williams, Chadd

Williams, Tiffani L.

Winkler, Manuela

Wismüller, Roland

Wiszniewski, Bogdan

Wolf, Wayne

Wolinski, Krisztof

Wong, Adam K.L.

Wook, Choi

Wu, Jie

Wu, Jiesheng

Xue, Jingling

Yahyapour, Ramin

Yang, Zhang

Yates, Kim

Yeung, Kwok Cheung

Yi, Qing

Yoo, Andy

Zahorjan, John

Zaki,

Zanichelli, Francesco

Zhang, Liang

Zhang, Yongbing

Zhou, Xiaobo (Joe)

Ziegler, Wolfgang

Zilles, Craig

Zima, Hans

Zimeo, Eugenio

Zlatev, Zahari

Zoccolo, Corrado

Zomaya, Albert

### **Table of Contents**

### **Invited Talks**

| Building Grid Applications and Portals:  An Approach Based on Components, Web Services and Workflow Tools.  D. Gannon, L. Fang, G. Kandaswamy, D. Kodeboyina, S. Krishnan,  B. Plale, and A. Slominski | 1  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Maintaining Thousands of In-Flight Instructions                                                                                                                                                        | 9  |

| Some Techniques for Automated, Resource-Aware Distributed and Mobile Computing in a Multi-paradigm Programming System  M. Hermenegildo, E. Albert, P. López-García, and G. Puebla                      | 21 |

| Why Structured Parallel Programming Matters                                                                                                                                                            | 37 |

| <b>Topic 1: Support Tools and Environments</b>                                                                                                                                                         |    |

| Topic 1: Support Tools and Environments                                                                                                                                                                | 38 |

| Profiling and Tracing OpenMP Applications with POMP Based Monitoring Libraries                                                                                                                         | 39 |

| Efficient Pattern Search in Large Traces Through Successive Refinement . F. Wolf, B. Mohr, J. Dongarra, and S. Moore                                                                                   | 47 |

| DRAC: Adaptive Control System with Hardware Performance Counters .<br>M. Pillon, O. Richard, and G. Da Costa                                                                                           | 55 |

| Reproducible Network Benchmarks with CONCEPTUAL                                                                                                                                                        | 64 |

| Optimizing Cache Access: A Tool for Source-to-Source Transformations and Real-Life Compiler Tests                                                                                                      | 72 |

| Detecting Data Races in Sequential Programs with DIOTA                                                                                                                                                 | 82 |

| A Time-Coherent Model for the Steering of Parallel Simulations                                                                                                                                         | 90 |

| MATE: Dynamic Performance Tuning Environment                                     | 98  |

|----------------------------------------------------------------------------------|-----|

| Imprecise Exceptions in Distributed Parallel Components                          | 108 |

| <b>Topic 2: Performance Evaluation</b>                                           |     |

| Topic 2: Performance Evaluation                                                  | 117 |

| Overhead Compensation in Performance Profiling                                   | 119 |

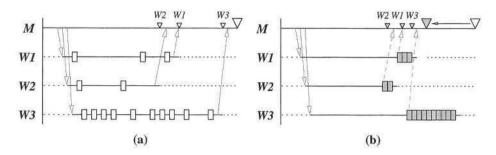

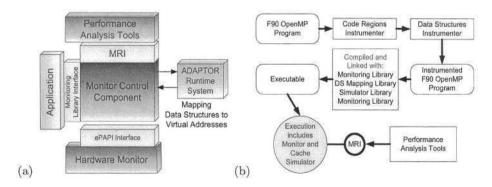

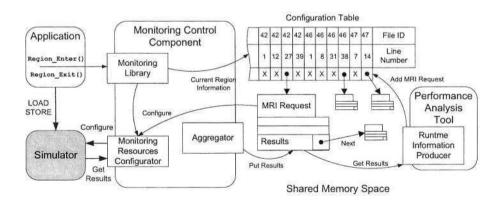

| A Data Structure Oriented Monitoring Environment for Fortran OpenMP Programs     | 133 |

| An Approach for Symbolic Mapping of Memory References                            | 141 |

| Impact of Cache Coherence Models on Performance of OpenMP Applications           | 149 |

| Evaluating OpenMP Performance Analysis Tools with the APART Test Suite           | 155 |

| Collective Communication Performance Analysis Within the Communication System    | 163 |

| Understanding the Behavior and Performance of Non-blocking Communications in MPI | 173 |

| Generation of Simple Analytical Models for Message Passing Applications          | 183 |

| Parallel Hybrid Particle Simulations Using MPI and OpenMP                        | 189 |

| Distributed Shared Memory: To Relax or Not to Relax?                             | 198 |

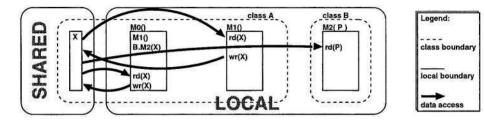

| Design-Time Data-Access Analysis for Parallel Java Programs with Shared-Memory Communication Model                                           | 206 |

|----------------------------------------------------------------------------------------------------------------------------------------------|-----|

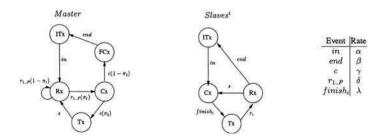

| Parallel PEPS Tool Performance Analysis Using Stochastic Automata Networks  L. Baldo, L.G. Fernandes, P. Roisenberg, P. Velho, and T. Webber | 214 |

| Topic 3: Scheduling and Load Balancing                                                                                                       |     |

| Topic 3: Scheduling and Load Balancing                                                                                                       | 220 |

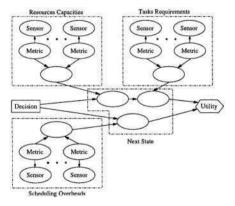

| Scheduling Under Conditions of Uncertainty: A Bayesian Approach $\dots$ $L.P.$ Santos and A. Proenca                                         | 222 |

| From Heterogeneous Task Scheduling to Heterogeneous Mixed Parallel Scheduling                                                                | 230 |

| Scheduling of MPI Applications: Self-co-scheduling                                                                                           | 238 |

| Scheduling Tasks Sharing Files from Distributed Repositories                                                                                 | 246 |

| A Scheduling Algorithm for Running Bag-of-Tasks Data Mining Applications on the Grid F.A.B. da Silva, S. Carvalho, and E.R. Hruschka         | 254 |

| Lookahead Scheduling for Reconfigurable GRID Systems                                                                                         | 263 |

| Topic 4: Compilers for High Performance                                                                                                      |     |

| Topic 4: Compilers for High Performance                                                                                                      | 271 |

| More Legal Transformations for Locality                                                                                                      | 272 |

| Link-Time Optimization of IA64 Binaries                                                                                                      | 284 |

| A Polyhedral Approach to Ease the Composition of Program Transformations                                                                     | 292 |

| for Improving Instruction TLB Energy Behavior  I. Kadayif, M. Kandemir, and I. Demirkiran                                                                               | 304                                           |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Using Data Compression to Increase Energy Savings in Multi-bank Memories                                                                                                | 310                                           |

| Automatic Customization of Embedded Applications for Enhanced Performance and Reduced Power Using Optimizing Compiler Techniques.<br>E. Özer, A.P. Nisbet, and D. Gregg | 318                                           |

| Architecture-Independent Meta-optimization by Aggressive Tail Splitting                                                                                                 | 328                                           |

| If-Conversion in SSA Form                                                                                                                                               | 336                                           |

| Topic 5: Parallel and Distributed Databases,                                                                                                                            |                                               |

| Data Mining and Knowledge Discovery                                                                                                                                     |                                               |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery  D. Skillicorn, A. Hameurlain, P. Watson, and S. Orlando                               | 346                                           |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery                                                                                        |                                               |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery                                                                                        | 347                                           |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery                                                                                        | 347<br>355                                    |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery                                                                                        | <ul><li>347</li><li>355</li><li>363</li></ul> |

| Topic 5: Parallel and Distributed Databases, Data Mining and Knowledge Discovery                                                                                        | <ul><li>347</li><li>355</li><li>363</li></ul> |

| Topic 6: Grid and Cluster Computing                                                                            |     |

|----------------------------------------------------------------------------------------------------------------|-----|

| Topic 6: Grid and Cluster Computing                                                                            | 398 |

| Agreement-Based Interactions for Experimental Science                                                          | 399 |

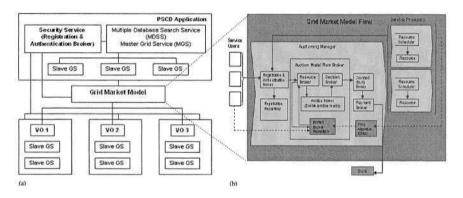

| A Double Auction Economic Model for Grid Services                                                              | 409 |

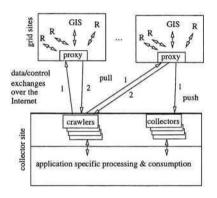

| Towards a Monitoring Framework for Worldwide Grid Information Services                                         | 417 |

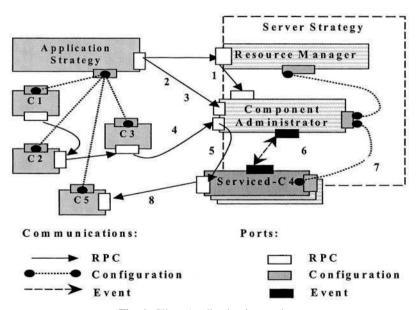

| A Model for a Component Based Grid-Aware Scientific Library Service S. Lombardo and A. Machì                   | 423 |

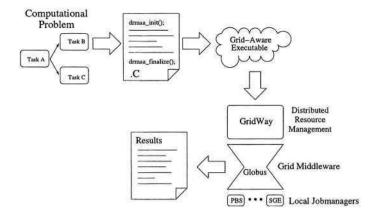

| Developing Grid-Aware Applications with DRMAA on Globus-Based Grids                                            | 429 |

| Exposing MPI Applications as Grid Services                                                                     | 436 |

| Globus-Based Grid Computing Simulations of Action Potential Propagation on Cardiac Tissues                     | 444 |

| Profiling Grid Data Transfer Protocols and Servers                                                             | 452 |

| Storage Power Management for Cluster Servers Using Remote Disk Access                                          | 460 |

| A Path Selection Based Algorithm for Maximizing Self-satisfiability of Requests in Real-Time Grid Applications | 468 |

| <b>Topic 7: Applications on High Performance Computers</b>                                                     |     |

| Topic 7: Applications on High Performance Computers                                                            | 476 |

| Using a Structured Programming Environment for Parallel Remote Visualization                                   | 477 |

| Parallel and Grid Computing in 3D Analysis of Large Dimmension Structural Systems                                                                      | 487 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| FlowVR: A Middleware for Large Scale Virtual Reality Applications  J. Allard, V. Gouranton, L. Lecointre, S. Limet, E. Melin, B. Raffin, and S. Robert | 497 |

| Topic 8: Parallel Computer Architecture and ILP                                                                                                        |     |

| Topic 8: Parallel Computer Architecture and Instruction-Level Parallelism                                                                              | 506 |

| Exploring the Possibility of Operating in the Compressed Domain  V. De La Luz, M. Kandemir, A. Sivasubramaniam, and M.J. Irwin                         | 507 |

| Contents Management in First-Level Multibanked Data Caches  E.F. Torres, P. Ibañez, V. Viñals, and J.M. Llabería                                       | 516 |

| A Mechanism for Verifying Data Speculation                                                                                                             | 525 |

| Feasibility of QoS for SMT                                                                                                                             | 535 |

| Improving Data Cache Performance via Address Correlation:  An Upper Bound Study                                                                        | 541 |

| Exploiting Spatial Store Locality Through Permission Caching in Software DSMs  H. Zeffer, Z. Radović, O. Grenholm, and E. Hagersten                    | 551 |

| CacheFlow: A Short-Term Optimal Cache Management Policy for Data Driven Multithreading                                                                 | 561 |

| SCISM vs IA-64 Tagging: Differences/Code Density Effects                                                                                               | 571 |

| <b>Topic 9: Distributed Systems and Algorithms</b>                                                                                                     |     |

| Topic 9: Distributed Systems and Algorithms                                                                                                            | 578 |

| Exploiting Differentiated Tuple Distribution in Shared Data Spaces G. Russello, M. Chaudron, and M. van Steen                                                                                | 579 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Enhancing Efficiency of Byzantine-Tolerant Coordination Protocols via Hash Functions                                                                                                         | 587 |

| Accelerating Apache Farms Through Ad-HOC Distributed Scalable Object Repository                                                                                                              | 596 |

| A Proxy Server-Network for Real-Time Computer Games                                                                                                                                          | 606 |

| Topic 10: Parallel Programming: Models, Methods and Languages                                                                                                                                |     |

| Topic 10: Parallel Programming:  Models, Methods and Programming Languages                                                                                                                   | 614 |

| Comparison of Parallelization Models for Structured Adaptive Mesh Refinement                                                                                                                 | 615 |

| Task-Queue Based Hybrid Parallelism: A Case Study                                                                                                                                            | 624 |

| Co-array Python: A Parallel Extension to the Python Language                                                                                                                                 | 632 |

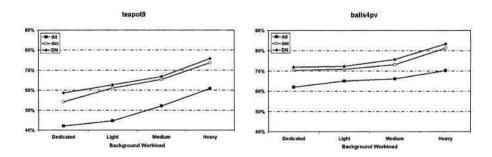

| Targeting Heterogeneous Architectures in ASSIST: Experimental Results .  M. Aldinucci, S. Campa, M. Coppola, S. Magini, P. Pesciullesi, L. Potiti, R. Ravazzolo, M. Torquati, and C. Zoccolo | 638 |

| A Fusion-Embedded Skeleton Library                                                                                                                                                           | 644 |

| Cross Component Optimisation in a High Level Category-Based Language  T.J. Ashby, A.D. Kennedy, and M.F.P. O'Boyle                                                                           | 654 |

| Concurrent Table Accesses in Parallel Tabled Logic Programs                                                                                                                                  | 662 |

| Handling Exceptions Between Parallel Objects                                                                                                                                                 | 671 |

| Parallel Software Interoperability by Means of CORBA in the ASSIST Programming Environment                                                                        | 679 |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Designing Parallel Operating Systems via Parallel Programming E. Frachtenberg, K. Davis, F. Petrini, J. Fernandez, and J. C. Sancho                               | 689 |

| Topic 11: Numerical Algorithms                                                                                                                                    |     |

| Topic 11: Numerical Algorithms                                                                                                                                    | 697 |

| Reducing the Deteriorating Effect of Old History in Asynchronous Iterations                                                                                       | 698 |

| Execution Schemes for Parallel Adams Methods                                                                                                                      | 708 |

| A Data Management and Communication Layer for Adaptive, Hexahedral FEM                                                                                            | 718 |

| A Parallel PSPG Finite Element Method for Direct Simulation of Incompressible Flow                                                                                | 726 |

| Load and Memory Balanced Mesh Partitioning for a Parallel Envelope Method                                                                                         | 734 |

| Combining Explicit and Recursive Blocking for Solving Triangular Sylvester-Type Matrix Equations on Distributed Memory Platforms                                  | 742 |

| Topic 12: High Performance Multimedia                                                                                                                             |     |

| Topic 12: High Performance Multimedia                                                                                                                             | 751 |

| Towards User Transparent Data and Task Parallel Image and Video Processing: An Overview of the Parallel-Horus Project F.J. Seinstra, D. Koelma, and A.D. Bagdanov | 752 |

| Visual Data Rectangular Memory                                                                                                                                    | 760 |

| Dynamic Granularity Switching in Parallel Block-Matching Motion Compensation                                       | 768  |

|--------------------------------------------------------------------------------------------------------------------|------|

| Placement of Nodes in an Adaptive Distributed Multimedia Server  B. Goldschmidt, T. Szkaliczki, and L. Böszörményi | 776  |

| A Practical Performance Analysis of Stream Reuse Techniques in Peer-to-Peer VoD Systems                            | 784  |

| Supporting Caching and Mirroring in Distributed Video-on-Demand Architectures                                      | 792  |

| An Efficient Fair Queuing Algorithm for Guaranteed Disk Bandwidth Y.J. Nam and C. Park                             | 799  |

| Topic 13: Theory and Algorithms for Parallel Computat                                                              | tion |

| Topic 13: Theory and Algorithms for Parallel Computation                                                           | 803  |

| Distributed Largest-First Algorithm for Graph Coloring                                                             | 804  |

| Parallel Delaunay Refinement with Off-Centers                                                                      | 812  |

| Near-Optimal Hot-Potato Routing on Trees                                                                           | 820  |

| A Coarse-Grained Parallel Algorithm for Spanning Tree and Connected Components                                     | 828  |

| Topic 14: Routing and Communication in Interconnection Networks                                                    |      |

| Topic 14: Routing and Communication in Interconnection Networks J. Duato, F. Petrini, O. Lysne, and A. Bilas       | 832  |

| Implementing MPI on the BlueGene/L Supercomputer                                                                   | 833  |

| S. Berrayana, E. Faure, D. Genius, and F. Pétrot                                                                                                                                                                                                                                                                                                     | 846        |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|

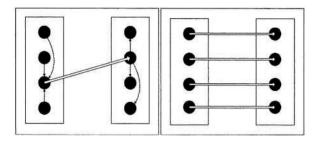

| OMULT: An Optical Interconnection System for Parallel Computing B.P. Sinha and S. Bandyopadhyay                                                                                                                                                                                                                                                      | 856        |

| Distributing InfiniBand Forwarding Tables                                                                                                                                                                                                                                                                                                            | 864        |

| Tuning Buffer Size in InfiniBand to Guarantee QoS                                                                                                                                                                                                                                                                                                    | 873        |

| Reducing Power Consumption in Interconnection Networks by Dynamically Adjusting Link Width                                                                                                                                                                                                                                                           | 882        |

| A Methodology to Evaluate the Effectiveness of Traffic Balancing Algorithms                                                                                                                                                                                                                                                                          | 891        |

| Load Unbalance in k-ary n-Cube Networks                                                                                                                                                                                                                                                                                                              | 900        |

| Understanding Buffer Management for Cut-Through 1D Rings                                                                                                                                                                                                                                                                                             | 908        |

| <b>Topic 15: Mobile Computing</b>                                                                                                                                                                                                                                                                                                                    |            |

| Topic 15: Mobile Computing                                                                                                                                                                                                                                                                                                                           | 916        |

| S.K. Das, J. Cao, J. Wu, and G. Ferrari                                                                                                                                                                                                                                                                                                              | 710        |

|                                                                                                                                                                                                                                                                                                                                                      |            |

| S.K. Das, J. Cao, J. Wu, and G. Ferrari  Coverage and Connectivity in Networks with Directional Sensors                                                                                                                                                                                                                                              | 917        |

| S.K. Das, J. Cao, J. Wu, and G. Ferrari  Coverage and Connectivity in Networks with Directional Sensors  E. Kranakis, D. Krizanc, and J. Urrutia  Local Route Recovery Algorithms for Improving Multihop TCP  Performance in Ad Hoc Wireless Networks                                                                                                | 917        |

| S.K. Das, J. Cao, J. Wu, and G. Ferrari  Coverage and Connectivity in Networks with Directional Sensors  E. Kranakis, D. Krizanc, and J. Urrutia  Local Route Recovery Algorithms for Improving Multihop TCP  Performance in Ad Hoc Wireless Networks  Z. Li and YK. Kwok  Cluster Based Distributed Mutual Exclusion Algorithms for Mobile Networks | 917<br>925 |

| UVOD: A Jini-Based Ubiquitous VOD Service Architecture  T.U. Choi and KD. Chung                                                          | 957  |

|------------------------------------------------------------------------------------------------------------------------------------------|------|

| Topic 16: Integrated Problem Solving Environments                                                                                        |      |

| Topic 16: Integrated Problem Solving Environments                                                                                        | 962  |

| Pattern/Operator Based Problem Solving Environments                                                                                      | 964  |

| Databases, Workflows and the Grid in a Service Oriented Environment Z. Jiao, J. Wason, W. Song, F. Xu, H. Eres, A.J. Keane, and S.J. Cox | 972  |

| A Parallel Programming Tool for SAR Processors                                                                                           | 980  |

| Topic 17: High Performance Bioinformatics                                                                                                |      |

| Topic 17: High Performance Bioinformatics                                                                                                | 988  |

| A Generic Parallel Pattern-Based System for Bioinformatics                                                                               | 989  |

| Parallel Inference of a 10.000-Taxon Phylogeny with Maximum Likelihood                                                                   | 997  |

| Cache-Based Parallelization of Multiple Sequence Alignment Problem G. Parmentier, D. Trystram, and J. Zola                               | 1005 |

| Topic 18: Peer-to-Peer and Web Computing                                                                                                 |      |

| Topic 18: Peer-to-Peer and Web Computing                                                                                                 | 1013 |

| The neast Primitive for Peer-to-Peer Networks                                                                                            | 1014 |

| A P2P Grid Services-Based Protocol: Design and Evaluation                                                                                | 1022 |

| A Synchronization and Session Control Based Protocol for 3D Multi-user Virtual Environments in a Peer-to-Peer Networks                   | 1032 |

### XXXIV Table of Contents

| Large-Scale Deployment in P2P Experiments                            |   |

|----------------------------------------------------------------------|---|

| Using the JXTA Distributed Framework 103                             | 8 |

| G. Antoniu, L. Bougé, M. Jan, and S. Monnet                          |   |

| Experimental Study of Multi-criteria Scheduling Heuristics           |   |

| for GridRPC Systems                                                  | 8 |

| Y. Caniou and E. Jeannot                                             |   |

| Using Similarity Groups to Increase Performance of P2P Computing 105 | 6 |

| J. Bourgeois, J.B. Ernst-Desmulier, F. Spies, and J. Verbeke         |   |

| Improving the Scalability                                            |   |

| of Logarithmic-Degree DHT-Based Peer-to-Peer Networks                | 0 |

| B. Carton and V. Mesaros                                             |   |

| A Small World Overlay Network for Resource Discovery                 | 8 |

| K. Vanthournout, G. Deconinck, and R. Belmans                        |   |

| <b>Author Index</b>                                                  | 7 |

|                                                                      |   |

### Building Grid Applications and Portals: An Approach Based on Components, Web Services and Workflow Tools

D. Gannon, L. Fang, G. Kandaswamy, D. Kodeboyina, S. Krishnan, B. Plale, and A. Slominski

Department of Computer Science, Indiana University Bloomington, Indiana, USA gannon@cs.indiana.edu http://www.extreme.indiana.edu

**Abstract.** Large scale Grid applications are often composed a distributed collection of parallel simulation codes, instrument monitors, data miners, rendering and visualization tools. For example, consider a severe storm prediction system driven by a grid of weather sensors. Typically these applications are very complex to build, so users interact with them through a Grid portal front end. This talk outlines an approach based on a web service component architecture for building these applications and portal interfaces. We illustrate how the traditional parallel application can be wrapped by a web service factory and integrated into complex workflows. Additional issues that are addressed include: grid security, web service tools and workflow composition tools. The talk will try to outline several important classes of unsolved problems and possible new research directions for building grid applications.

#### 1 Introduction

This talk will consider the basic problem of building Grid applications by composing web services and CCA components in a dynamic, distributed environment. There are three basic issues that we address. First we consider the way the user accesses the Grid applications. It is our experience that this is best accomplished with a web portal that can provide the user with a secure framework for accessing all his or her applications and services. The design of such a portal is non-trivial and plays a central role in the overall security architecture of the Grid. The second important problem is to provide a way for the user to encapsulate legacy applications as Grid services that can be securely accessed by remote, authorized clients. Finally we consider the problem of integrating dynamic workflow with the static composition model of component frameworks like the Common Component Architecture. In this extended abstract we briefly consider each of these problems.

### 2 The Portal

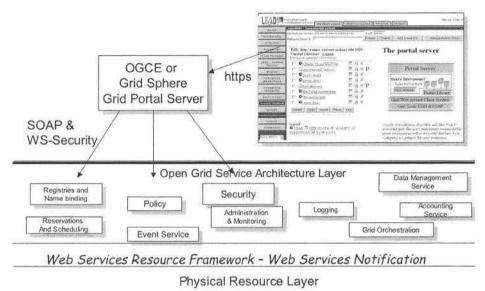

There is a four layer model that can best illustrate the role of the portal in its relation to the user and Grid/web services. At the bottom layer we have the physical resources

that comprise the Grid fabric. At the layer above that we have a core service framework like WSRF or OGSI, which provides the common language to talk about the real and virtual resources of the Grid. Above that we have the Open Grid Service Architecture , which is s set of specifications for the common Grid services that applications use. Finally the Portal Server provides the gateway for the user. The portal server provides the environment in which the user 's "grid context" is established. This server is based on emerging standards [11] and is available from OGCE [15] or the GridSphere [14] project.

**Fig. 1.** Users access the portal via a standard web browsers. The portal server becomes the proxy for the user in his or her interactions with the Grid.

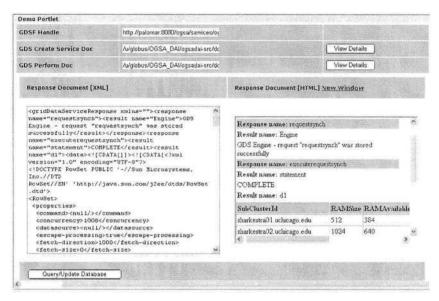

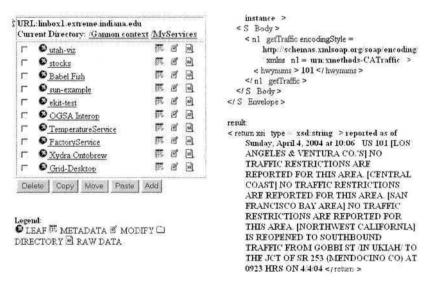

The OGCE and GridSphere portal servers are each based on the concept of "portlets", which are portal components that each provide a specialized capability, such as access to some service. For example, the OGSA Data Access and Integration service is a Grid service to access databases and metadata services. Figure 2 illustrates the portlet that is presented to the user from the portal server.

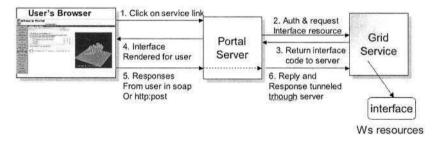

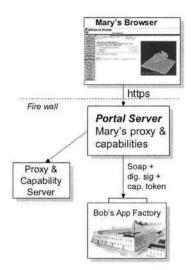

Users access the portal via a web browser over https, so they can be assured their interaction with the portal server are secure. The portal server fetches and hold the user's proxy credentials, so that it can act on the user behalf for the duration of the session. An important special case where the portal acts as the agent for the user while interacting with the Grid, is when a Grid service must project a user interface to the user. The way this is accomplished is illustrated in Figure 3.

The user first makes a request to the portal server to load the interface for the protected Grid Service. The portal server then calls the service in question using the user's credentials and asks for the service interface. The Grid service stores this interface as a standard service resource. It may be an HTML form document or it may be an applet. The portal delivers this interface back to the user. The user uses the interface to formulate a query for the remote service and sends that back to the portal server which tunnels it to the service.

Fig. 2. The OGSA DAI portlet allows user to pose queries to Grid data services.

Fig. 3. Using the portal server to tunnel service requests to the back-end Grid services.

It should be noted that this model is very similar to WSRP [12], but it places the emphasis on security and using the built-in capability of WSRF or OGSI. WSRP is an OASIS standard for building Remote Portlets for Web Services. Our approach, which is based on dynamically loading interfaces into the portal server has some advantages. First, it allows the service to define the interface in the same way that a web site defines the way it presents itself to users. But, most important, loading the interface first into the portal server, allows that interface to share the users portal context information. This context information includes security credentials, such as proxy certificates and capability tokens.

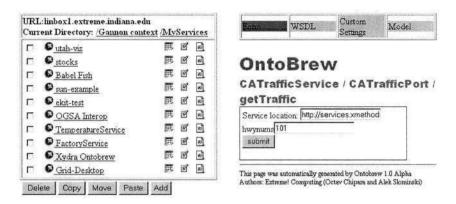

It is also possible for the portal to generate an interface for simple web services automatically. Octav Chipara and Aleksander Slominski developed Xydra Ontobrew [21], (see figure 4 and 5) which can dynamically load a WSDL file that defines a web service and generate an interactive interface for it. While it does not work in cases where message have extremely complex types, it works in those cases where the service may be designed for human interaction.

#### D. Gannon et al.

**Fig. 4.** OntoBrew is a portal component that automatically generates a human interface for a web service, given its WSDL definition. In this case we see the California Highway Traffic Information Service.

Fig. 5. The result of the query to the traffic service for information about Highway 101.

We find the portal layer is one of the most important parts of the Grid system because it is where the user meets the Grid services. If it is not designed well, the users will not use the Grid at all. There must be a clear advantage to using the portal over dealing with the Grid in terms of basic distributed computing primitives. In fact, for scientific users, they will use the portal only if it has something that can be accessed with three or fewer mouse clicks and is something that they can access no other way.

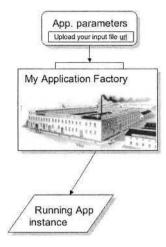

**Fig. 6.** The application factory model. The factory presents a user interface to the user through the portal that allows the user to supply any configuration parameters needed by the application prior to its execution.

# 3 Incorporating Legacy Applications Using a Factory Service

Legacy applications are an important part of almost all large scale Grid application. The challenge for legacies is to incorporate them as components into larger workflows and composed applications. One solution is to provide a Factory service, as illustrated in Figure 6, that is capable of launching instances of the application based on parameters supplied to the factory by the user.

There are two significant issues that are important here. The first is that it is most application scientists are not trained in writing web services and a mechanism is needed to help them do this. Fortunately, it is possible to write a factory generator that can live within the portal server and can be used to create a factory on behalf of the application programmer. What the programmer must provide is a simple xml document that describes the application and its configuration parameters and how it is launched. From this information we can automatically generate a factory service for the application.

The second issue is solving the problem of how to authorize other users to use a factory service. Unlike most services, which run as "root", the factory service runs with the identity of the application program that created it. The solution we use is to allow the owner of the factory service to create capability tokens which allow certain users, or groups of users access to the factory. These tokens are simple xml documents that are signed by the owner of the service stating that the intended user shall have the authorization to interact with the owner's factory.

As shown in Figure 7, these capabilities can be stored in a separate capability store and a user's capabilities can be fetched by the portal each time the user logs into the portal. The ability to encapsulate an application, and provide secure access and authorization to it, is very similar in spirit to the original Netsolve and Ninf projects [4, 13], which pioneered the concept of viewing an application as a service.

Fig. 7. Users access the portal via a standard web browsers. The portal server becomes the proxy for the user in his or her interactions with the Grid.

# 4 Workflow and Component Composition

There are a host of good workflow tools for scientific Grid applications including Dagman [5], ICENI [8], Triana [18], Keppler and Ptolemy II [17], Taverna and GridAnt [19]. On the industrial side there is BPEL4WS [3]. In addition there are component based software systems like CCA [2, 16, 23]. In the presentation we will focus on two aspects of doing workflow in Grid systems. First we will illustrate a large and complex example motivated by mesoscale storm simulation [6] and then we will discuss the interesting challenges of compiling very high level graphical specifications into one or more of the languages listed above.

There are a host of open problems for research in Grid Programming in general. (See [22] for a good overview). In the area of component based systems, there are two general models: dataflow based composition (Triana and Ptolemy are good examples of this), in which as stream of data is pushed from a source port to a destination port and remote procedure call (RPC) based systems like CCA a source invokes a function on the remote side and waits for a response. In both cases, the underlying assumption is that a source and destination port are both live partners in a data exchange. Workflow systems sequence activities and the connection between component services may only be a causal dependence. However this is not always the case. Modern web services allows us to send a message to one service and ask that the reply be sent to different service. This is possible because most web services operate on a message level rather than RPC. However, CCA can be implemented using web services (see XCAT3 [23]) and we can build workflows that incorporate both models.

Most of the tools for Grid workflow assume that the user wants to build the workflow as a simple graph of service component. However, this compact graph model is not always appropriate. This may be the case when the workflow is simply too large and complex to effectively "program" it as a graph. (However, some tools allow one

to turn a Graph into a new first-class component or service, which can then be included as a node in another graph (a workflow of workflows). This technique allows graphs of arbitrary complexity to be constructed). But size complexity is not the only problem. It may be the case that the workflow is driven by events that determine its structure. It may also be the case that the workflow structure is defined by processes that are negotiated at runtime. For example, suppose one component service must be replaced by another and that new service requires other new services to be connected into the picture. These new services may also require a different organization of the upstream components of the workflow. Or, for example, a workflow may be able to dynamically optimize its structure when it sees that a component service is not needed. While applications of workflows of this complexity may appear to be science fiction at the present time, the application of Grids to autonomic systems may require this level of intelligence and adaptability.

Finally, the static graph model may fail as a means to characterize the workflow in the case that the graph is implicit as in the case when the workflow is expressed as a set of desired outcomes that can be satisfied by a number of different workflow enactments. For example, a data query may be satisfied moving a large data set across country or it may be cheaper to recreate the data in a local environment. This is a simple example of the Griphyn virtual data concept.

For larger systems, or for workflows of most complex dynamically structured type, something that resembles a complete programming language is required. BPEL4WS is the leading candidate for a "complete programming language" for workflows. In fact, BPEL provides two usage patterns for expressing workflow behaviors. The first usage pattern is based on the concept of an abstract process which represents a role, such as "buyer" or "seller" in a business process and the "graph" based language to describe their interaction. These interactions are defined by partner links and BPEL provides the language to describe the public aspects of the protocol used in the interaction between these partners. The other usage pattern of BPEL involves the "algebraic" language needed to define the logic and state of an executable process in terms of web service resources and XML data, and tools to deal with exceptions and failures.

There are a number of significant general issues for workflow authoring and enactment in Grid systems. Many of these point to general research problems for the future.

One area that has received little attention in the current Grid workflow projects is the issue of security. It is dangerous to trust a complex workflow enactment to assure that resources are protected. To what extent is a single user's identity/authority sufficient to authroize a complex workflow enactment that may require a large set of capabilities to complete a set of distributed tasks?

Another interesting area of research involves the way in which we can use a workflow document as part of the scientific provenance of a computational experiment? Under what conditions can we publish a workflow script as a document that can be used by others to verify a scientific claim? If the workflow was triggered by sequences of external events, can the monitoring of the workflow capture these events well enough so that the enactment can be repeated?

There are many other interesting questions. Can we build systems that allow workflows to automatically do incremental self-optimization? Can we automatically discover new properties and services of a Grid that enable such self-optimization? If there is time, we will address additional issues in the final presentation.

#### References

- Agarwal, M., and Parashar, M. . Enabling Autonomic Compositions in Grid Environments. Proceedings of the 4th International Workshop on Grid Computing (Grid 2003), Phoenix, AZ, USA, IEEE Computer Society Press, pp 34 - 41, November 2003.

- Armstrong, R., Gannon, D., Geist, A., Keahey, K., Kohn, S. McInnes, L., Parker, S., and Smolinski, B.. Towards a common component architecture for high performance scientific computing. In *Proceedings of the The Eighth IEEE International Symposium on High Per*formance Distributed Computing, 1998.

- 3. Business Process Execution Language for Web Services Version 1.1. http://www-106.ibm.com/developerworks/library/ws-bpel/

- 4. Casanova, H. and Dongarra, J, NetSolve: a network server for solving computational science problems. Proceedings SC 96.

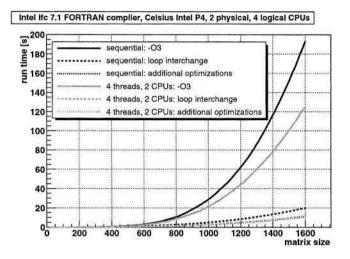

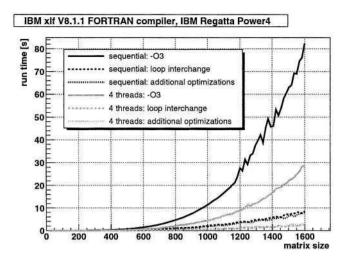

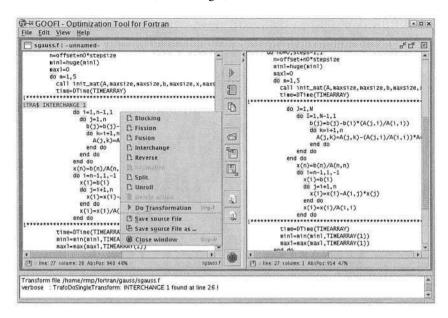

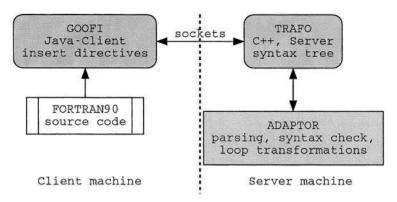

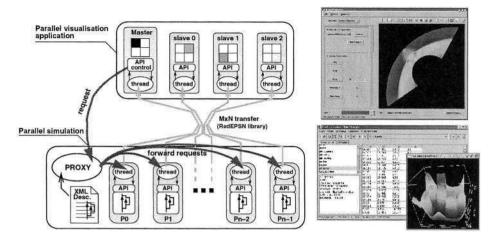

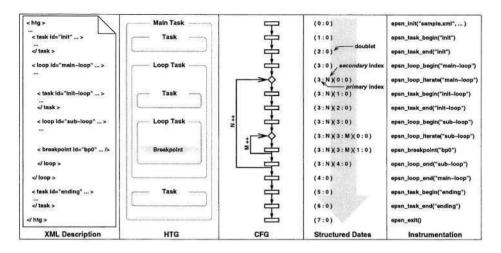

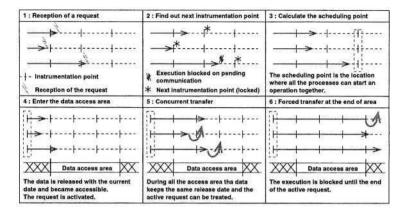

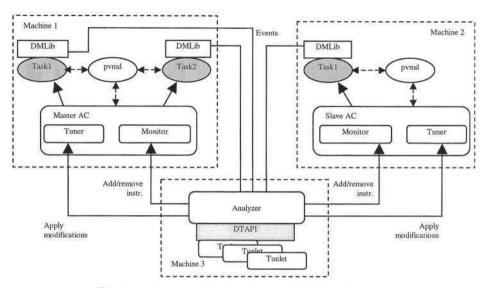

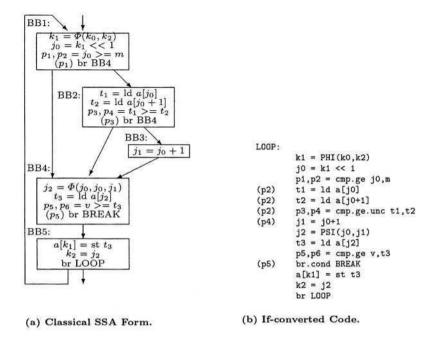

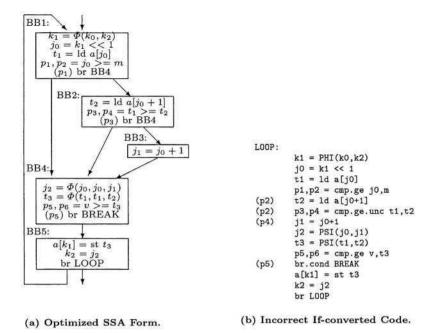

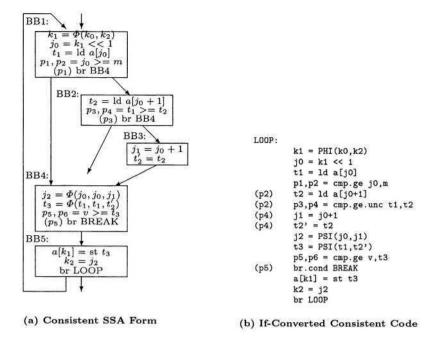

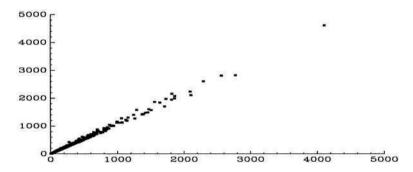

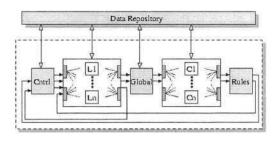

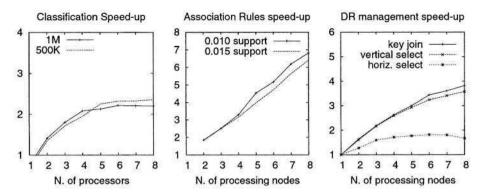

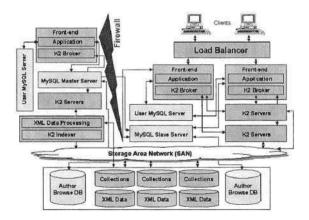

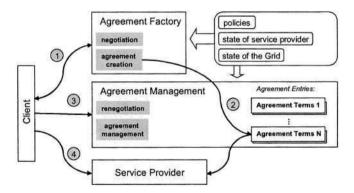

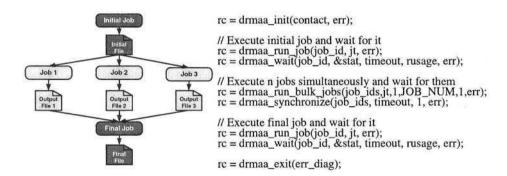

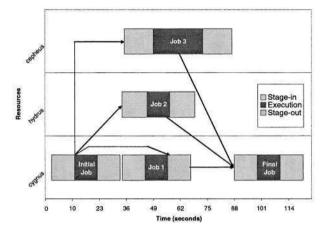

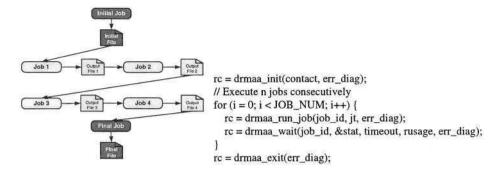

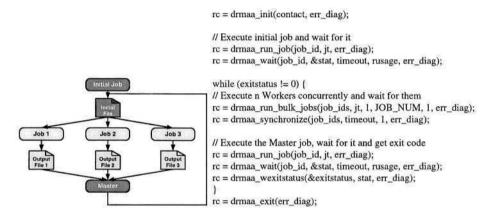

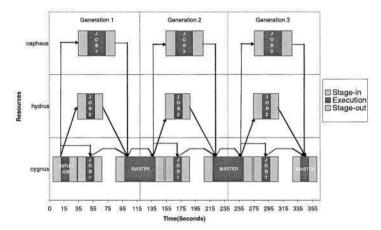

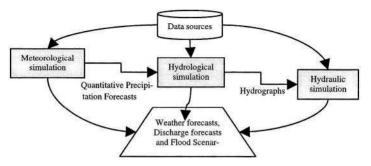

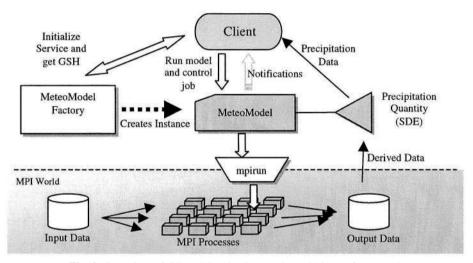

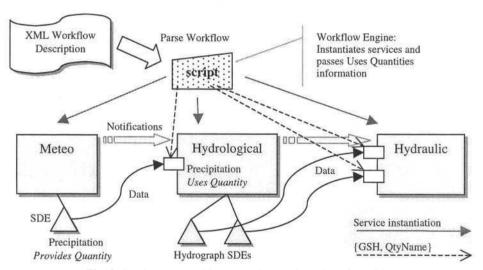

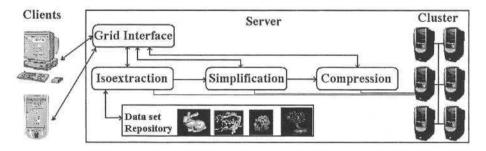

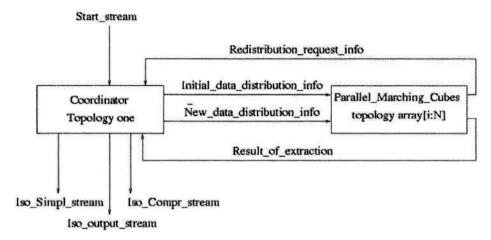

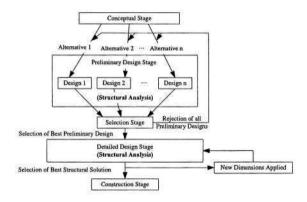

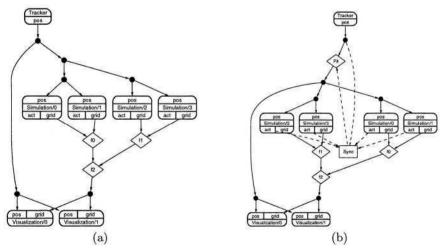

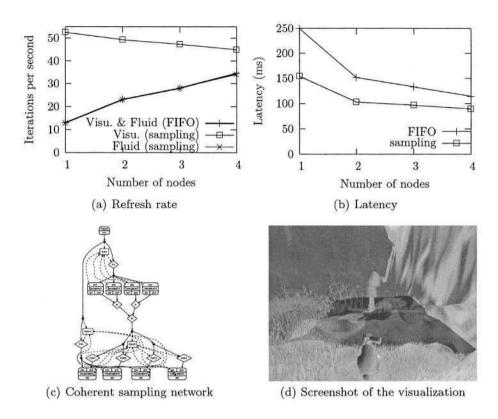

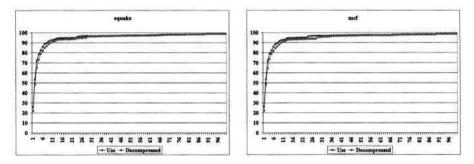

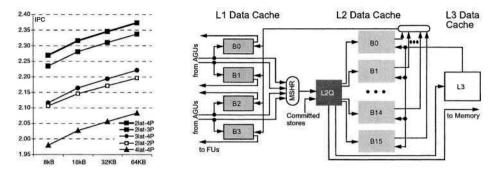

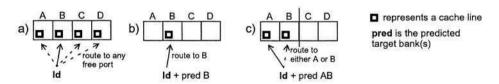

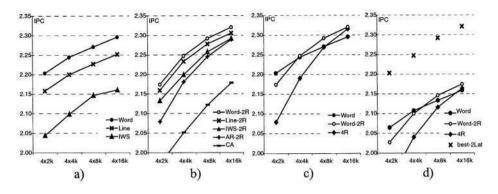

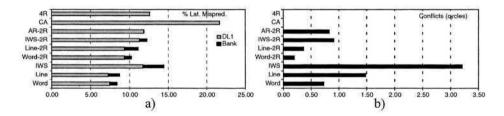

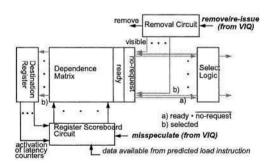

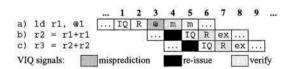

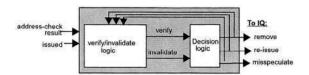

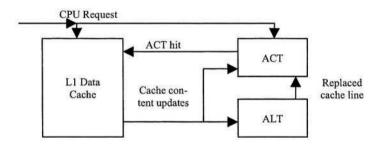

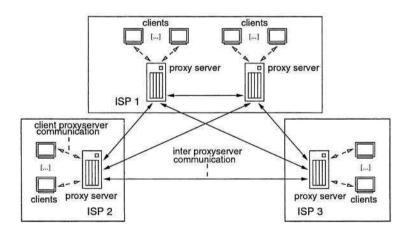

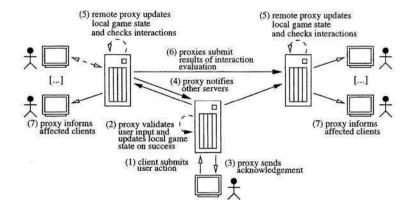

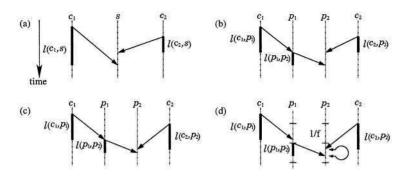

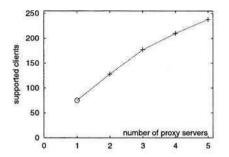

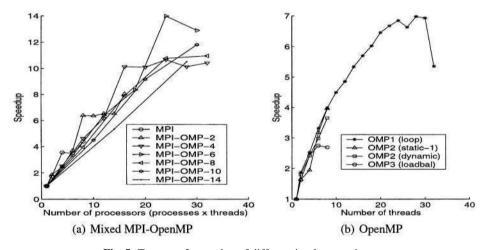

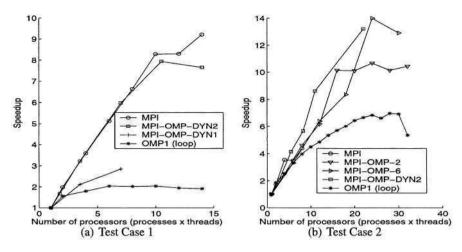

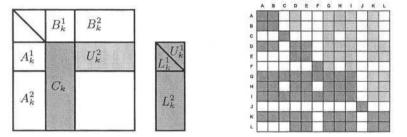

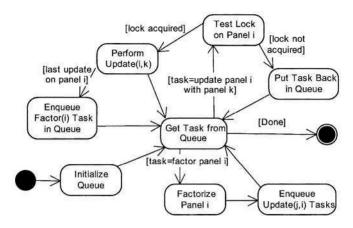

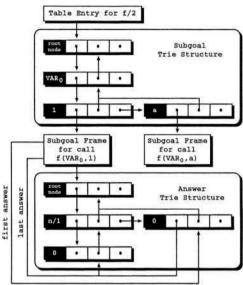

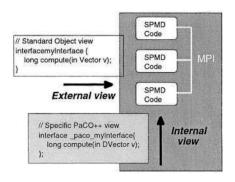

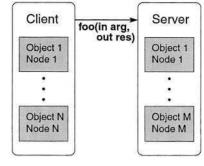

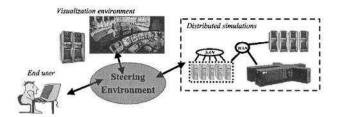

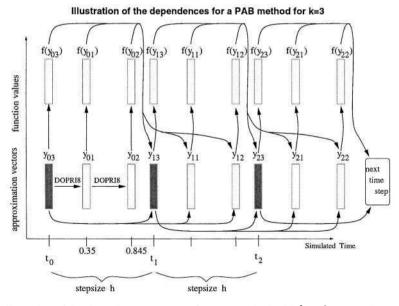

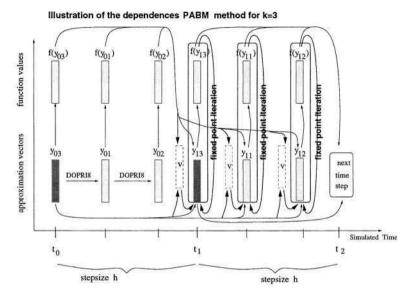

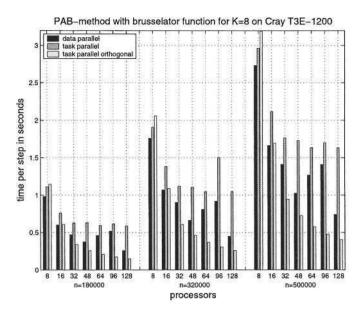

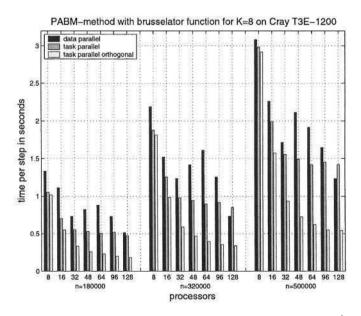

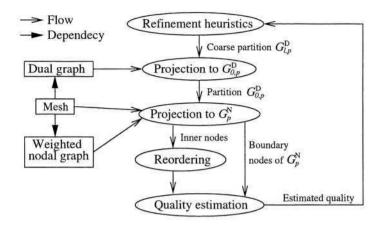

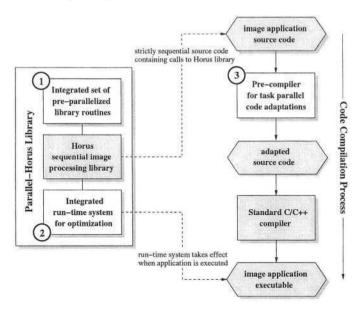

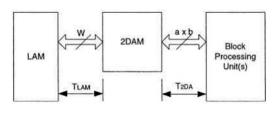

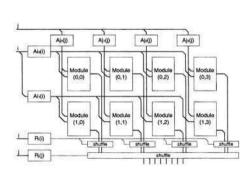

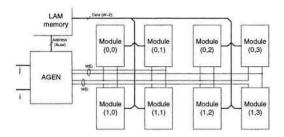

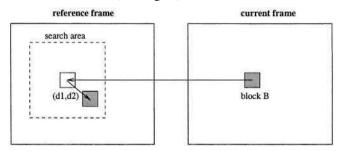

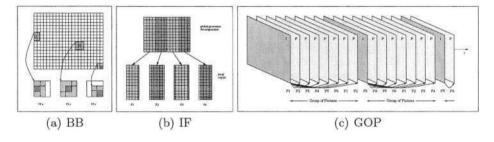

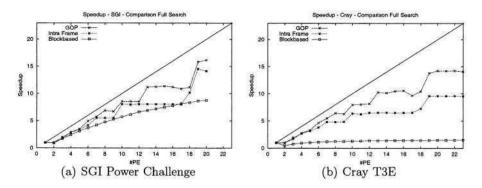

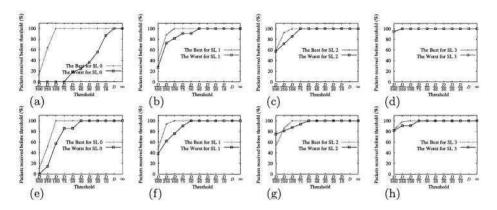

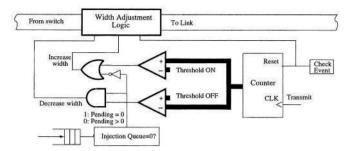

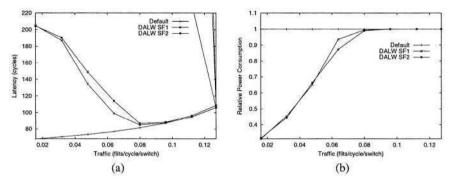

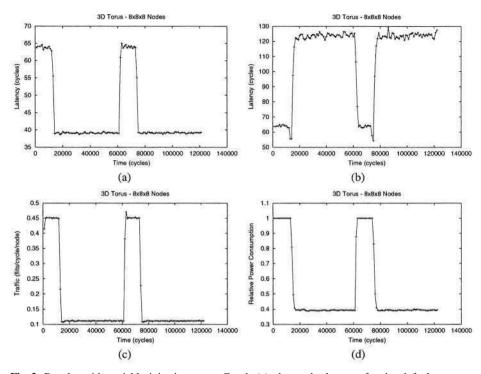

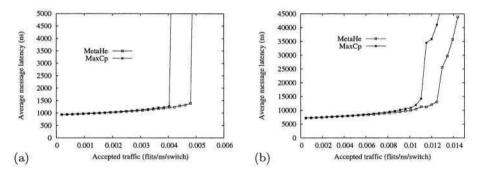

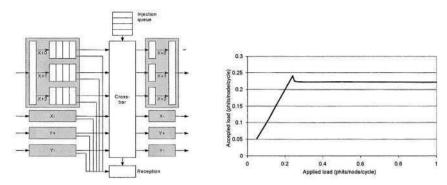

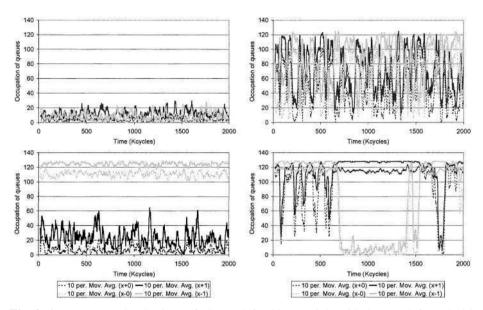

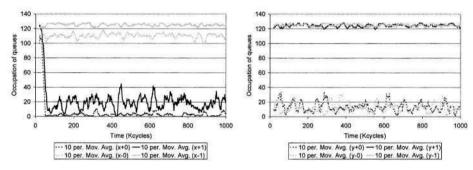

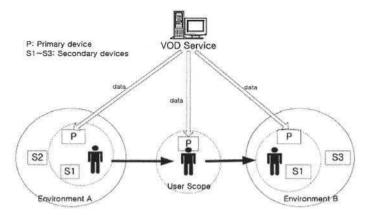

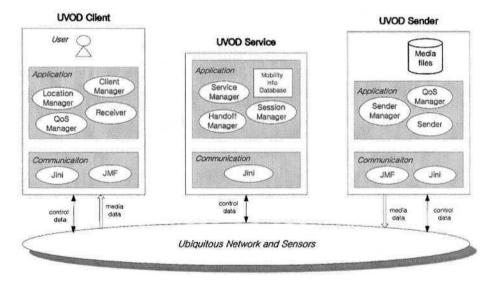

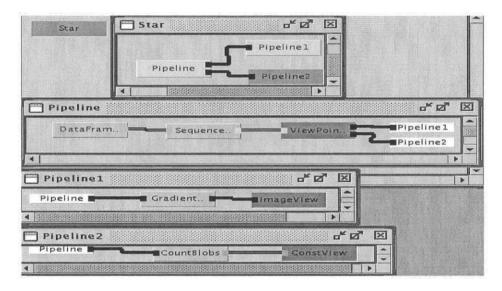

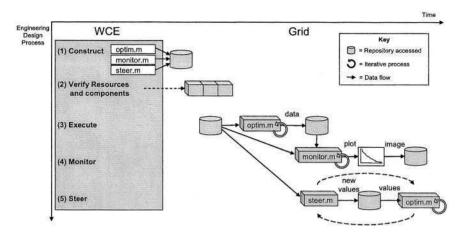

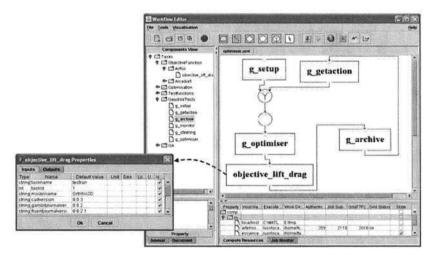

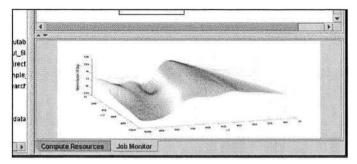

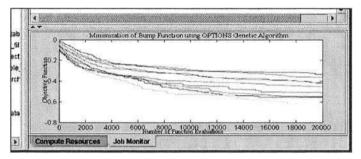

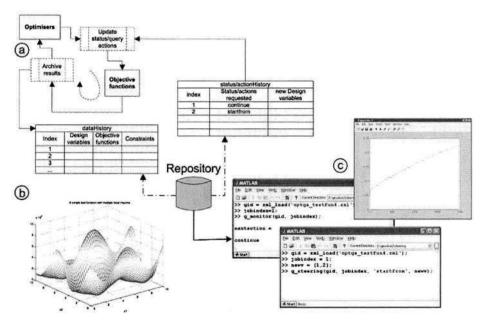

- 5. Condor Dagman, http://www.cs.wisc.edu/condor/dagman/